はじめに

以前の記事では、オペアンプを使用したD-A変換回路を説明しました。

本記事では、逆に、A-D変換回路を紹介します。

並列比較型A-D変換器と二重積分型A-D変換器の2種類あります。

コンパレータ(比較器)の知識が前提として必要ですので、まずそこから解説していきます。

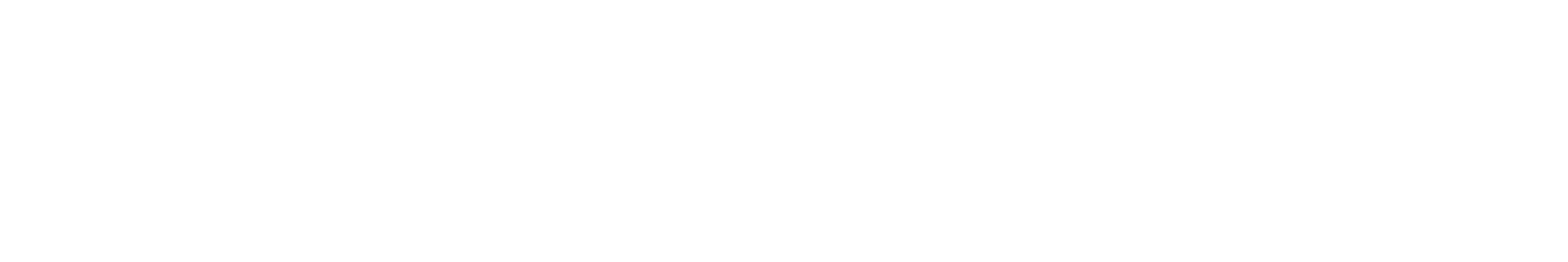

オペアンプを使用したコンパレータ

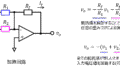

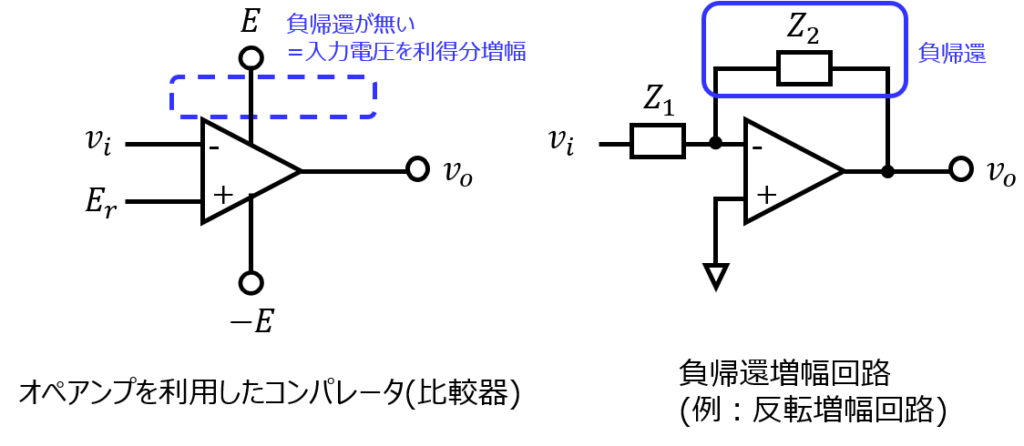

端的に言うと、負帰還が無いオペアンプを言います。

図で言うと、出力電圧のラインが入力電圧のラインと繋がっていない回路構成を指しています。

オペアンプは、入力電圧を増幅する素子です。

発振条件の記事でも紹介しましたが、一般的に負帰還を用いて出力電圧とのフィードバックを用いながら、目標の出力電圧に制御します。

しかし、今回はそれが無いです。

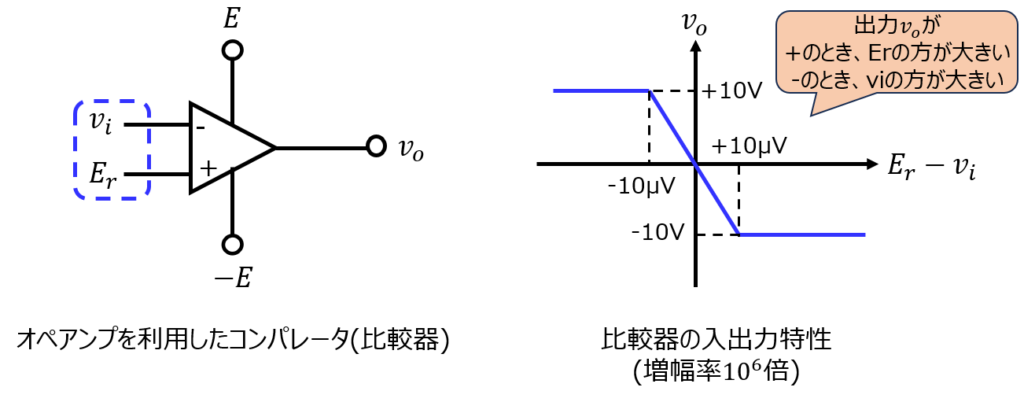

ですので、入力電圧が正ならば+∞。入力電圧が負ならば-∞方向へ理論上発散します。

実際には、外部電源±Eの制約から、上下限は±Eで留まりますが、少しでも入力が正(負)なら、その方向へ発散していくことが分かります。

よって、比較相手の電圧\(E_{r}\)を-極に入力し、入力電圧\(v_{i}\)を+極に入力すると、下記の関係が生まれます。

- \(v_{i}>E_{r}\)のとき、出力は正 (+E)

- \(v_{i}<E_{r}\)のとき、出力は負 (-E)

細かい電圧差でも増幅するため、出力電圧を見るとどっちの方が大きいかは一目瞭然です。

このような考え方で、オペアンプは入力の増幅だけでなく、比較器としても扱うことができるのでした。

オペアンプを使用したA-D変換器

並列比較型A-D変換器

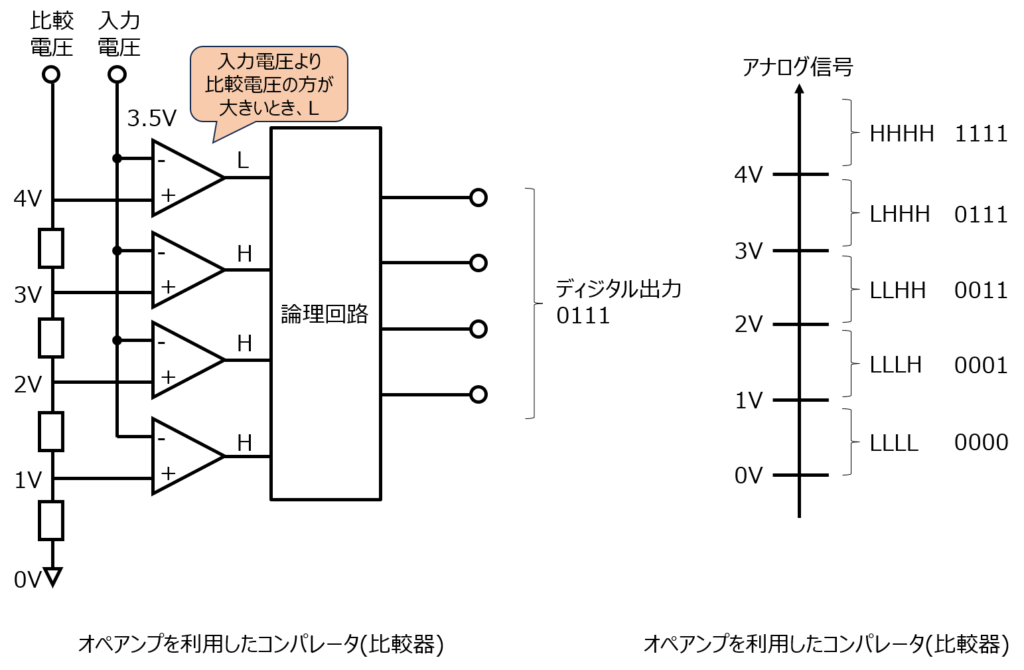

前章で説明したコンパレータの応用です。

同じく、比較電圧\(E_{r}\)とアナログ電圧を入力する構成に変わりありませんが、直列に繋がっています。

また、オペアンプの間には、比較電圧側には抵抗が存在します。

すると、どうなるでしょうか。

比較電圧側は、下の段に行くほど電圧が下がります。よって、一番上の段では\(v_{i}<E_{r}\)で0(FALSE)だった出力が、どこかの段でTRUEになりそうです。

このように、アナログ入力信号の大きさによって、01のbitを割り当てることで、デジタル変換を実現していることが分かりました。

並列比較型A-D変換器の特徴

入力電圧を多くのオペアンプ(比較器)で一度に変換することから、下記の利点、欠点があります。

- 動作が高速であること。

- 分解能を細かくするほど、大きのオペアンプ、抵抗が必要になる。

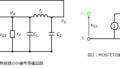

二重積分型A-D変換器

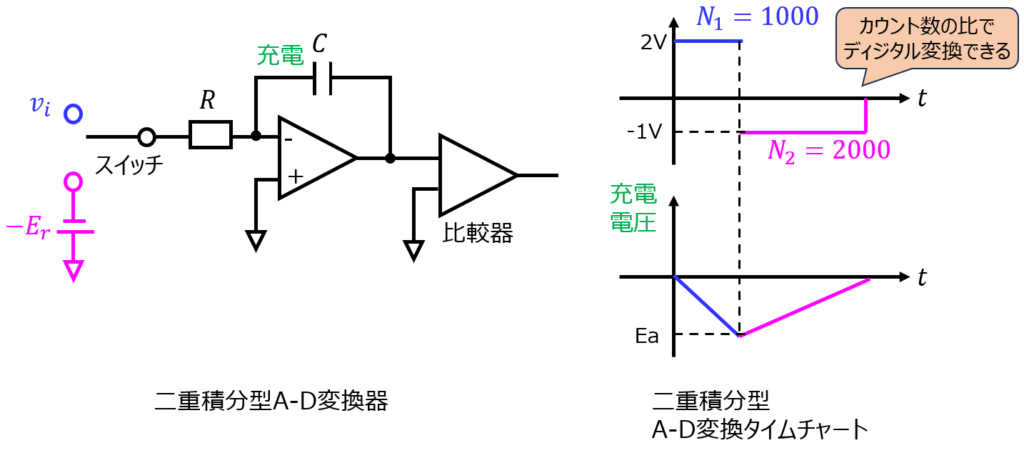

入力電圧\(v_{i}\)をある一定のカウント数コンデンサに対しかけ続けると、その分だけ充電します。

次に、比較電圧\(E_{r}\)を逆側からかけたとき、コンデンサの電圧が0になるまでのカウント数=相殺にかかった時間の比を用いてデジタル変換します。

下記に原理図を示します。

最初、スイッチを1側に倒して置き、入力電圧\(v_{i}\)を\(N_{1}\)カウント分かけ続けます。結果、コンデンサには電圧\(E_{a}\)までかかったとします。

次に、スイッチを2側に倒し、比較電圧\(E_{r}\)を逆側からかけます。\(N_{2}\)カウント後、コンデンサにかかる電圧が0になったとすると、下記の関係が成立します。

\begin{aligned}v_{i}T_{1}=E_{r}T_{2} \\ v_{i}=E_{r}\dfrac{T_{2}}{T_{1}}\end{aligned}

\(E_{r}\)と\(T_{1}\)は既知であるため、ディジタル量\(N_{2}\)でアナログ量\(v_{1}\)を表すことができました。

二重積分型A-D変換器の特徴

並列比較型と比較して下記の利点、欠点があります。

- 高精度であること。(並列比較型は、段数を大きくするほど上下の段との電圧差が小さくなるので、ノイズの影響を受けやすい。)

- 積分時間が必要なので、変換速度が遅い

最後に

本記事は、あまり院試では出てきません。ですが、D-A変換器を紹介する以上、逆の紹介もした方が良いと考え、記事作成しました。

将来、デバイス技術者になることを考えている方は覚えておくと良いかもしれません。